Генерация кода Verilog из модели

Генерация кода Verilog из модели

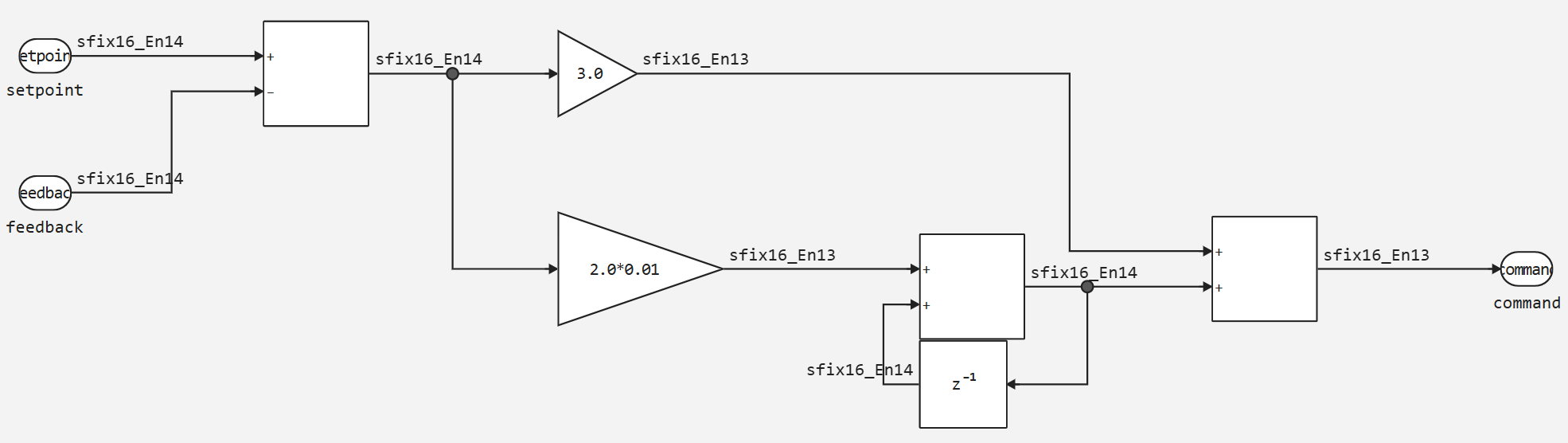

В данном примере используется модель из следующей демонстрации https://engee.com/helpcenter/stable/ru/interactive-scripts/base_simulation/PID_fixed.html, и, учитывая применение в ней типов данных с фиксированной точкой, мы можем себе позволить сгенерировать из них код на языках Verilog. Код будем генерировать из блока PID-регулятора.

Теперь сгенерируем из этой модели код на языке Verilog. Для этого в функции программного управления генератором кода зададим атрибут target="verilog".

Verilog — это язык описания аппаратуры (HDL), используемый для проектирования и моделирования цифровых систем, таких, как схемы ПЛИС и ASIC. Он позволяет описывать структуру и поведение цифровых схем на уровне регистров и логики, что делает его основным инструментом для инженеров в сфере аппаратного обеспечения. Verilog поддерживает моделирование параллельных процессов, что критично для схем с большим количеством одновременно работающих компонентов.

Основные сферы применения Verilog перечислены ниже.

-

Проектирование ПЛИС и ASIC: Verilog позволяет описывать сложные цифровые системы, которые затем можно синтезировать в физические схемы на ПЛИС или интегральных схемах.

-

Симуляция и верификация: Verilog предоставляет возможность симуляции, позволяя тестировать и отлаживать схемы перед их реализацией на аппаратуре.

-

Автоматизация разработки: синтезаторы переводят Verilog-код в оптимизированные логические схемы, что упрощает процесс создания и тестирования аппаратных компонентов.

Verilog применяется в проектах, требующих высокоскоростной обработки данных и надежного параллельного выполнения.

engee.generate_code("$(@__DIR__)/pid_fixed.engee", "$(@__DIR__)/verilog"; subsystem_name="SubSystem", target="verilog")

Теперь проанализируем результаты.

Как мы видим, код был успешно сгенерирован и может быть применён в дальнейшей разработке, сам код представлен ниже.

module pid_fixed_SubSystem(

input clock,

reset,

input [15:0] io_setpoint,

io_feedback,

output [15:0] io_command

);

reg [15:0] UnitDelay_state;

wire [15:0] _AddAccum_T = io_setpoint - io_feedback;

wire [28:0] _Gain_2_new_T_1 = {{13{_AddAccum_T[15]}}, _AddAccum_T} * 29'hA4;

wire [29:0] _Gain_new_T_1 = {{14{_AddAccum_T[15]}}, _AddAccum_T} * 30'h6000;

wire [15:0] _Add_1Accum_T = {_Gain_2_new_T_1[28:14], 1'h0} + UnitDelay_state;

always @(posedge clock) begin

if (reset)

UnitDelay_state <= 16'h0;

else

UnitDelay_state <= _Add_1Accum_T;

end // always @(posedge)

assign io_command = _Gain_new_T_1[29:14] + {_Add_1Accum_T[15], _Add_1Accum_T[15:1]};

endmodule

Вывод

В данном примере мы рассмотрели возможности генерации кода в Engee и показали вам, как применять этот инструмент для ваших проектов.