HDL FIFO

将输入采样序列存储在先进先出(FIFO)寄存器中。

模块类型: SubSystem

库中的路径: |

港口

输入

#

在

—

数据输入信号

标量,标量

Details

块中输入数据的信号。

当向块写入数据时,最新的数据被放置在寄存器的末尾。 块记录此记录之后的后续数据。

| 数据类型 |

|

| 复数支持 |

是的 |

#

推,推

—

记录控制信号

标量,标量

Details

值到达此端口时 1,该块将来自*In*端口的数据放在FIFO寄存器的末尾。

| 数据类型 |

|

| 复数支持 |

非也。 |

#

流行乐

—

读取控制信号

标量,标量

Details

值到达此端口时 1,该块从FIFO寄存器中卸载第一个元素,并将此值保存在*Out*端口上。

| 如果在同一时间步长触发两个或多个控制输入端口,则首先读取*Pop*信号,然后写入*Push*信号。 |

| 数据类型 |

|

| 复数支持 |

非也。 |

#

rst

—

复位控制信号

标量,标量

Details

当复位端口接收到值 1,它重置*Empty*,Full*和*Num*块的输出 *HDL FIFO.

| 数据类型 |

|

| 复数支持 |

非也。 |

输出

#

出

—

数据输出信号

标量,标量

Details

FIFO块的数据输出信号。 当从FIFO执行读操作时,首先写入FIFO寄存器的数据从FIFO中提取并保持在输出端。

| 数据类型 |

|

| 复数支持 |

是的 |

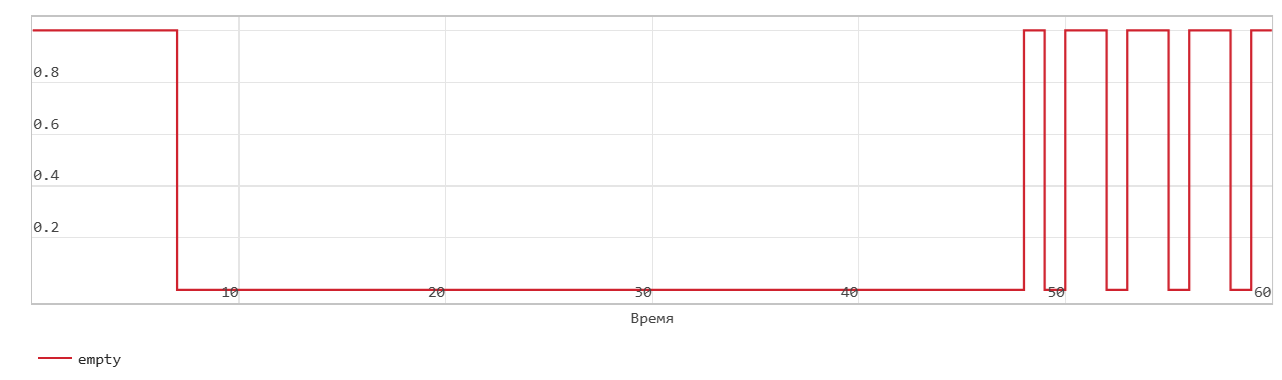

#

恩普里

—

空寄存器指示信号

标量,标量

Details

FIFO输出的控制信号等于 1 当FIFO寄存器中没有数据并且不可能执行读操作时。

| 数据类型 |

|

| 复数支持 |

非也。 |

#

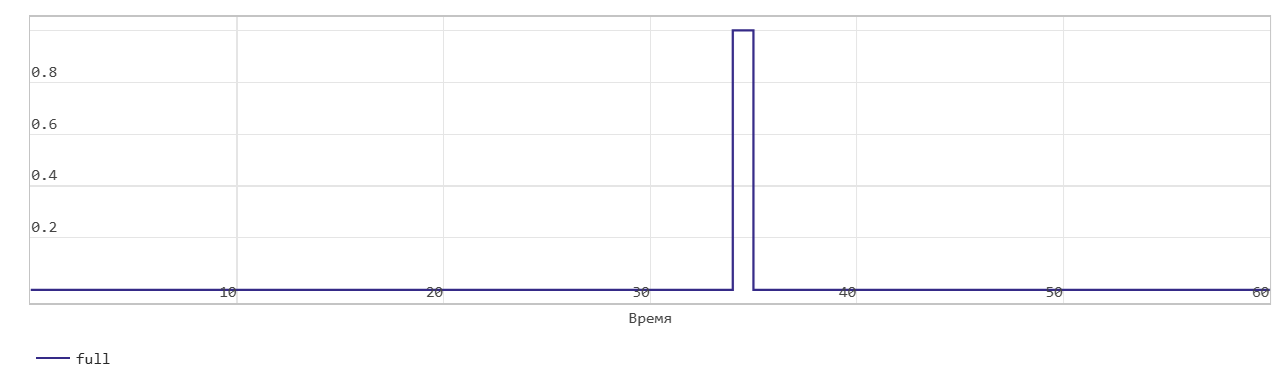

全

—

登记册满度的单一指示

标量,标量

Details

FIFO输出的控制信号,其 1 当FIFO寄存器已满且不能接受更多数据时。

| 数据类型 |

|

| 复数支持 |

非也。 |

#

Num

—

参赛作品数目

标量,标量

Details

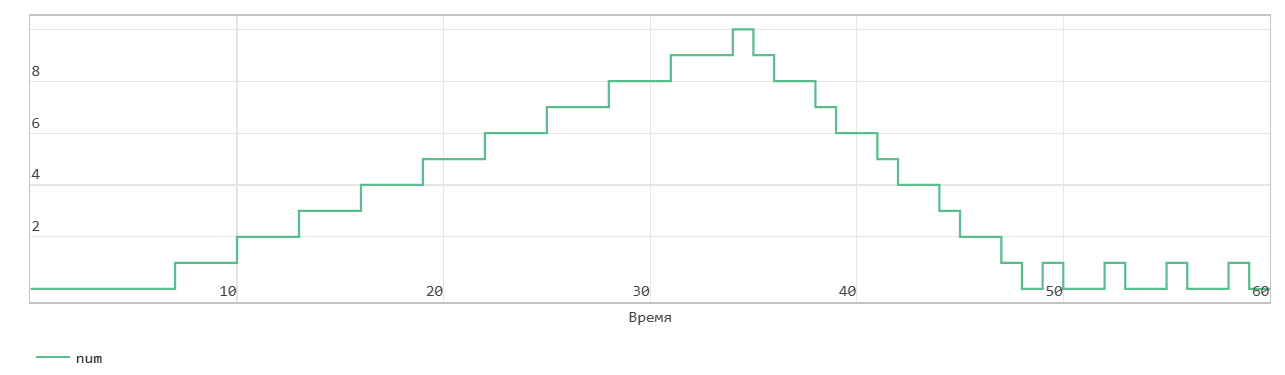

当前在FIFO寄存器中的数据量。

**Num*增加 1 对于您写入FIFO的每个数据。

**Num*减少 1 对于从FIFO读取的每个数据。

| 数据类型 |

|

| 复数支持 |

非也。 |

参数

主组

# Register size — 参赛作品数目

Details

指定可包含FIFO寄存器的记录数。

的最小值 Register size – 4.

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

#

Mode —

操作模式

Classic | FWFT

Details

指定FIFO操作模式。

使用模式 FWFT 您可以向前看并查看FIFO队列前面的数据,而无需执行读取操作。 模式 FWFT 当您使用AXI4-Stream接口施加背压时,它特别有用。

| 值 |

|

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# The ratio of output sample time to input sample time — 采样率因子

Details

指定输出处的采样周期与输入处的采样周期之比。

默认情况下,此比率为 1,这意味着*In*和*Push*输入以及*Out*和*Pop*输出以相同的采样率运行。

输入和输出可以在不同的采样周期下工作。 使用正整数或 1/N,在哪里 N -正整数。 例如,如果输入 1/2,那么输出的采样周期将比输入的采样周期少两倍,即输出的工作速度会更快。 端口*Full*、*Empty*和*Num*的信号以更高的速度运行。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

#

Push onto full register —

推送端口上的溢出情况

Ignore | Warning | Error

Details

指定块在写入填充FIFO时应如何反应。

| 值 |

|

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

#

Pop empty register —

Pop端口上的溢出条件

Ignore | Warning | Error

Details

指定块应如何响应从空FIFO读取。

| 值 |

|

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# On empty register indicator port (Empty) — 空寄存器显示端口

Details

选择此选项可启用空寄存器显示端口。

此端口输出 1 当FIFO寄存器为空,并 0 当FIFO包含一个或多个数据记录时。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# On full register indicator port (Full) — 寄存器满度指示端口

Details

选择此选项可启用寄存器填充指示端口。

此端口输出 1 当FIFO寄存器已满时。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# On number of register entries port (Num) — 关于寄存器中的条目数的信息的端口

Details

选择此选项以启用有关寄存器中条目数的信息端口。

此端口输出FIFO队列中当前可用的数据量。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# On local reset port (rst) — 本地复位端口

Details

选择此选项以启用额外的本地重置端口*rst*。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

信号设置

#

Data type —

数据类型

Float64 | Float32 | Float16 | Int8 | UInt8 | Int16 | UInt16 | Int32 | UInt32 | Int64 | UInt64 | Int128 | UInt128 | Bool | Fixed-point

Details

指定数据类型。 设置为:

-

漂浮64 -

漂浮物32 -

漂浮物16 -

Int8 -

UInt8 -

Int16 -

UInt16 -

Int32 -

UInt32 -

Int64 -

UInt64 -

Int128 -

UInt128 -

布尔 -

定点

| 值 |

|

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# Data fixed-point type — 定点数据类型

Details

指定定点数据类型。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

#

Signal type —

信号类型

Real | Complex

Details

指定信号的类型。 设置为:

-

真实的 -

综合体

| 值 |

|

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

# Sample time — 采样周期

Details

的采样周期,设置为正数。

| 默认值 |

|

| 程序使用名称 |

|

| 可调谐 |

无 |

| 可计算 |

是 |

算法

FIFO写操作

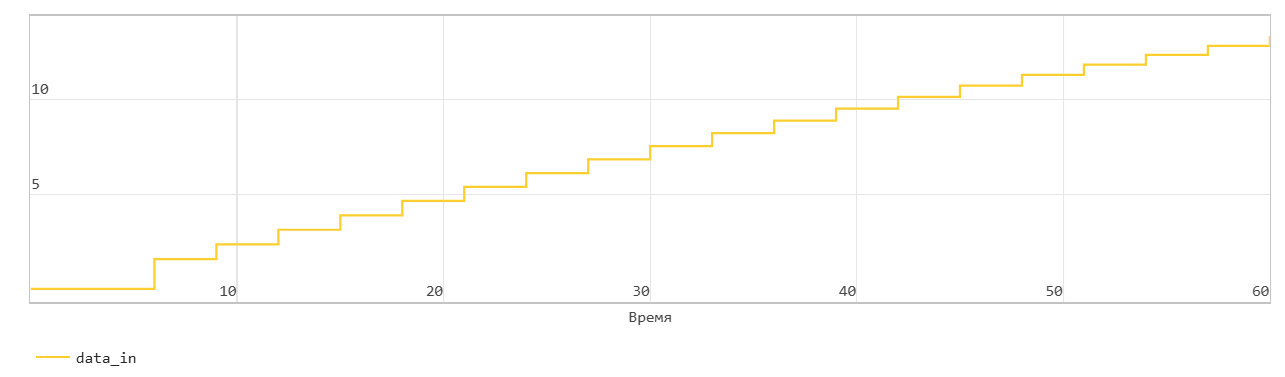

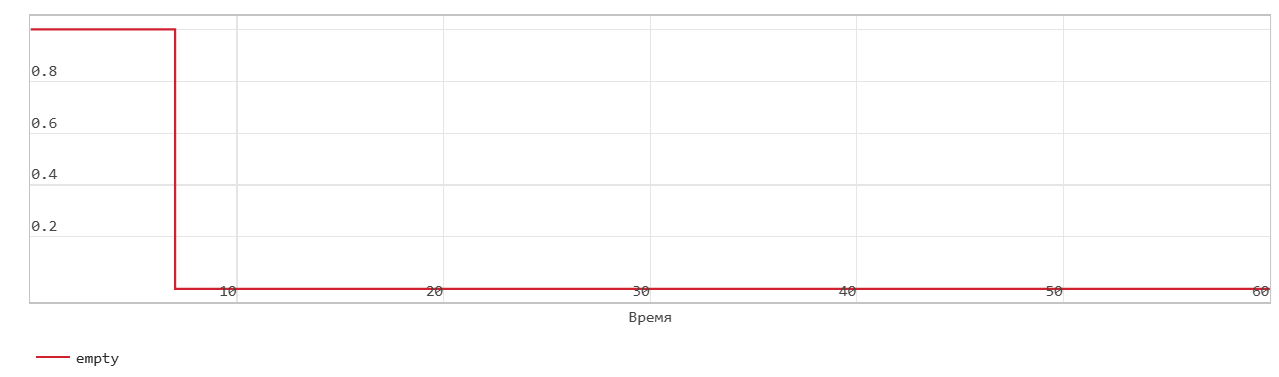

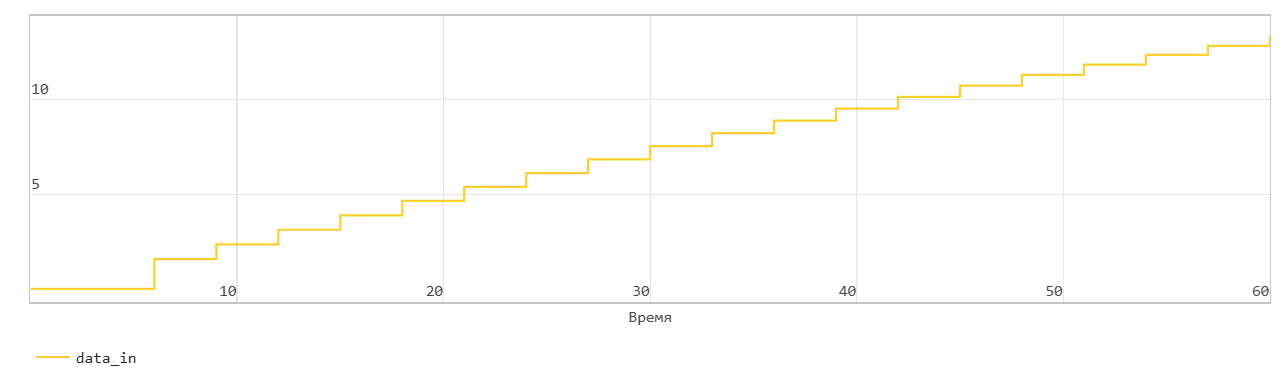

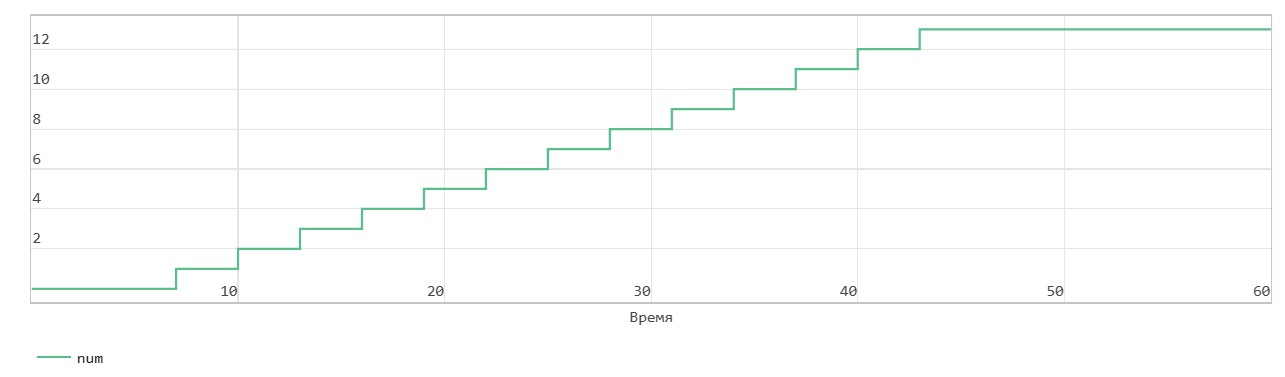

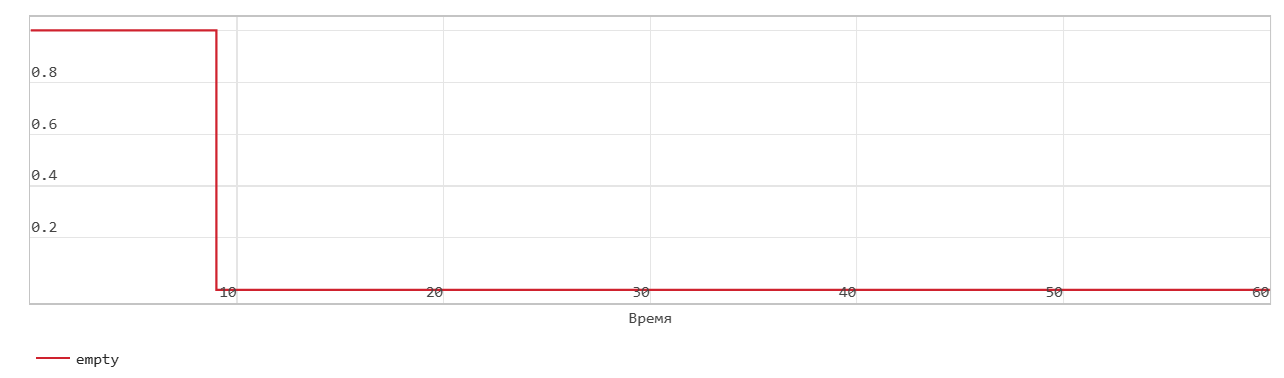

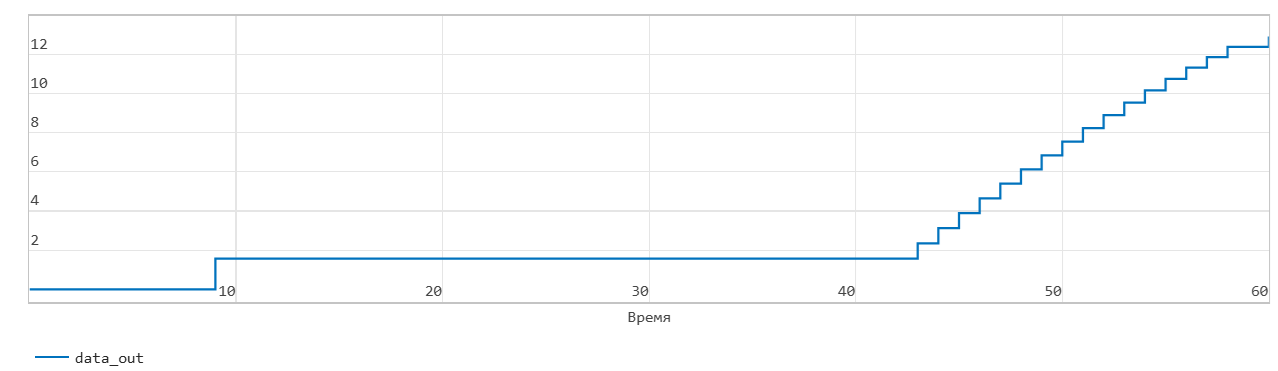

这张图显示了写操作。 *Push*输入端口作为写操作的使能信号。 在图中,*data_in*表示此信号。

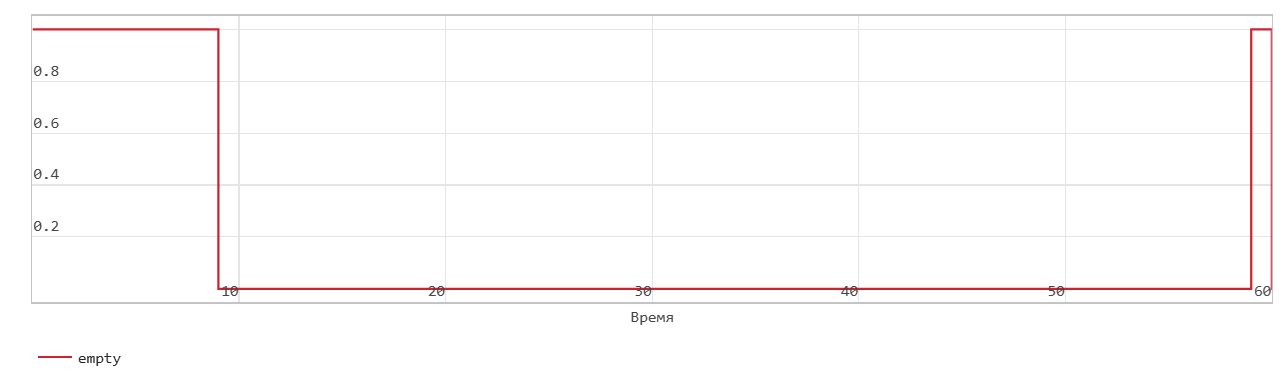

当信号*data_in*等于 0,该块不向FIFO写入数据,而是设置*Empty*标志。

当*data_in*信号变得相等 1,该块在下一时间步中将*In*输入端口上的*din*信号转换到FIFO寄存器的末尾。 *Num*信号表示FIFO寄存器中的数据量。 每次将数据写入FIFO时,*Num*信号增加 1. 在时间步 6 *data_in*等于 1. 在下一个时间步骤中,*data_in*等于 7,数据写入FIFO。 *Num*信号增加 1,并且*Empty*标志被取消。

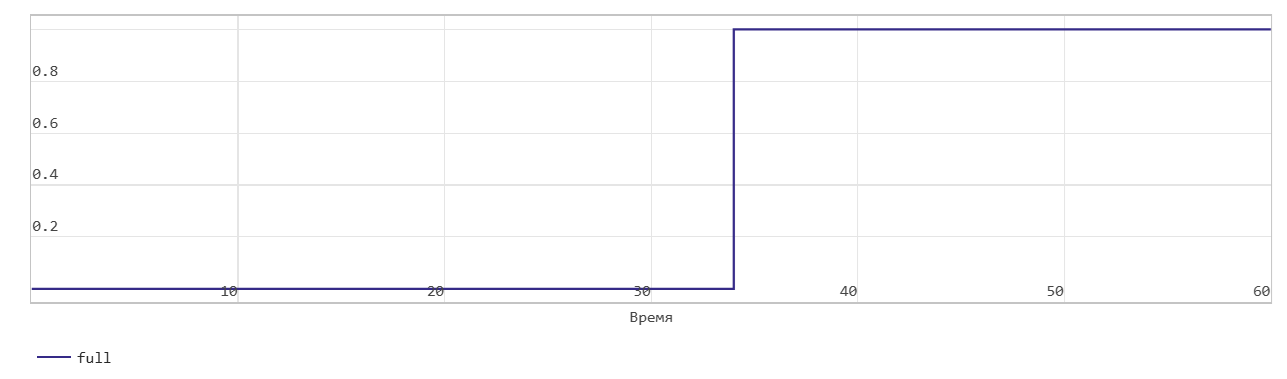

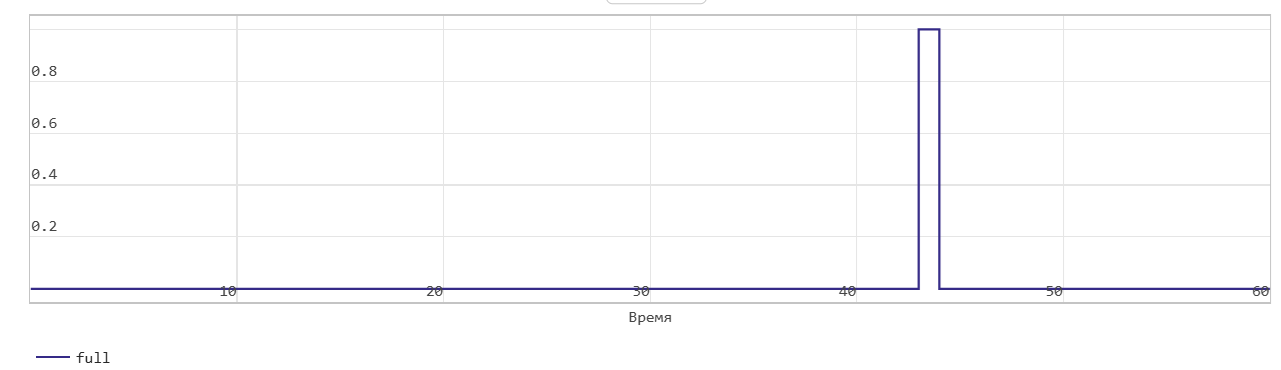

该FIFO使用*Register size*参数指定的寄存器大小。 默认情况下,寄存器大小为 10. 在图中,当*Num*信号变得相等 10 在时间步 34,给出了*Full*信号。 在*Full*信号变得相等之后 1 如果将更多数据写入FIFO,则该块生成警告。

经典FIFO读操作

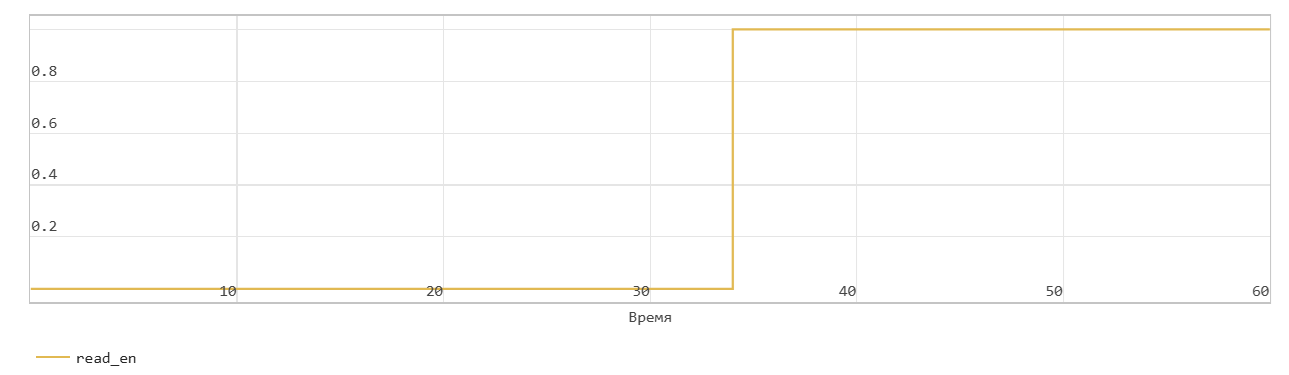

此图显示了读取操作。 *Pop*输入端口作为读操作的使能信号。 在图中,*read_en*表示此信号。

图中显示当*read_en*信号为 1 在时间步 34 *dout*信号在下一时间步输出FIFO中最旧的记录 35. *Full*标志未选中,*Num*信号减少 1 从时间步开始 35 作为数据从FIFO中读取。

当*Num*信号变得相等 0,给出*空*信号。 后*空*信号变为相等 0 如果从FIFO读取更多数据,则该块生成警告。

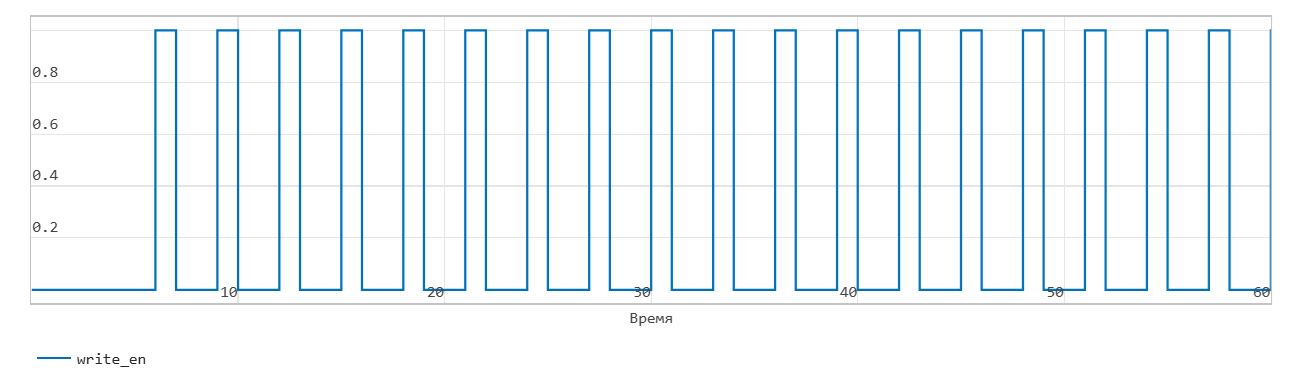

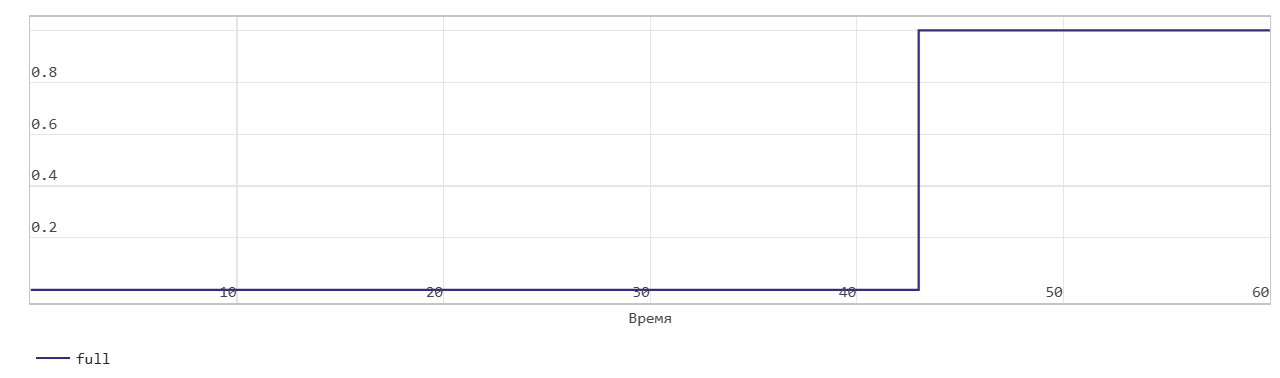

通过FIFO写入第一个字的操作

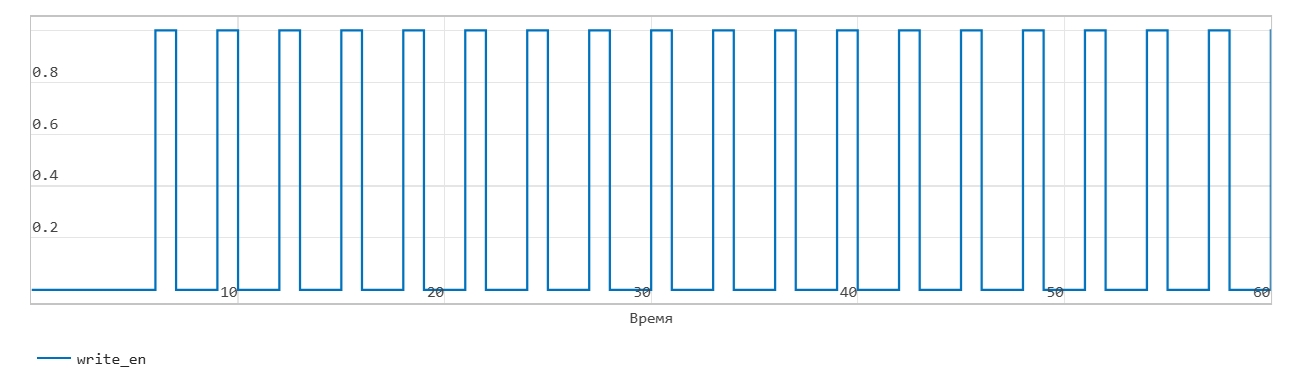

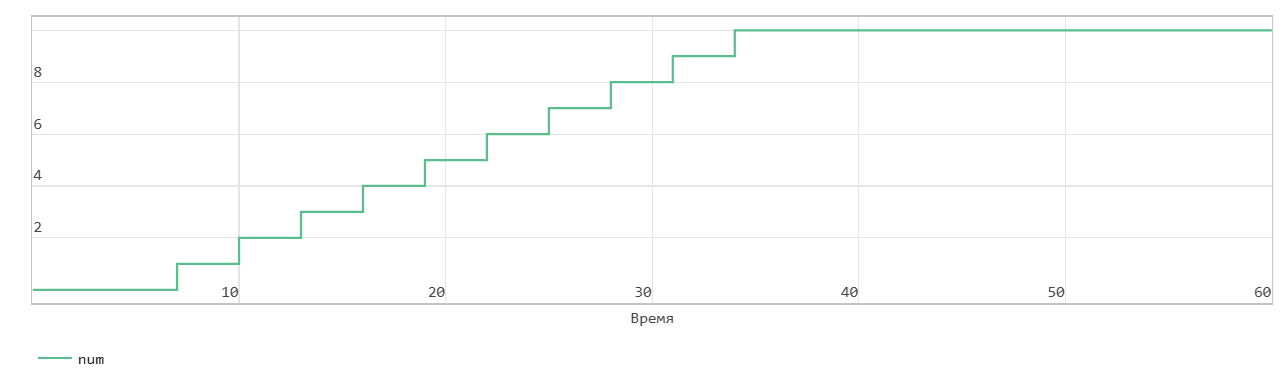

此图显示了*Mode*参数设置为时的录制操作 FWFT. *Push*输入端口作为写操作的使能信号。 在图中,*write_en*表示此信号。

当*write_en*信号等于 0,该块不向FIFO写入数据并设置*空*标志。

当*write_en*信号变得相等 1,该块在下一时间步中将输入端口*In*上的*din*信号的值转换到FIFO寄存器的末尾。 *Num*信号表示FIFO寄存器中的数据量。 每次将数据写入FIFO时,*Num*信号增加 1. 在时间步 6,*write_en*等于 1. 在下一个时间步骤中 7,数据写入FIFO。 *Num*信号增加 1,并且*Empty*标志被取消。

FIFO使用Register size参数指定的寄存器大小。 默认情况下,寄存器大小为 10. 在图中,当*Num*信号变得相等 13 在时间步 43,给出了*Full*信号。 在FWFT模式下,FIFO可以存储更多 3 超出其设定大小的值。 在*Full*信号变得相等之后 1 如果将更多数据写入FIFO,则该块生成警告。

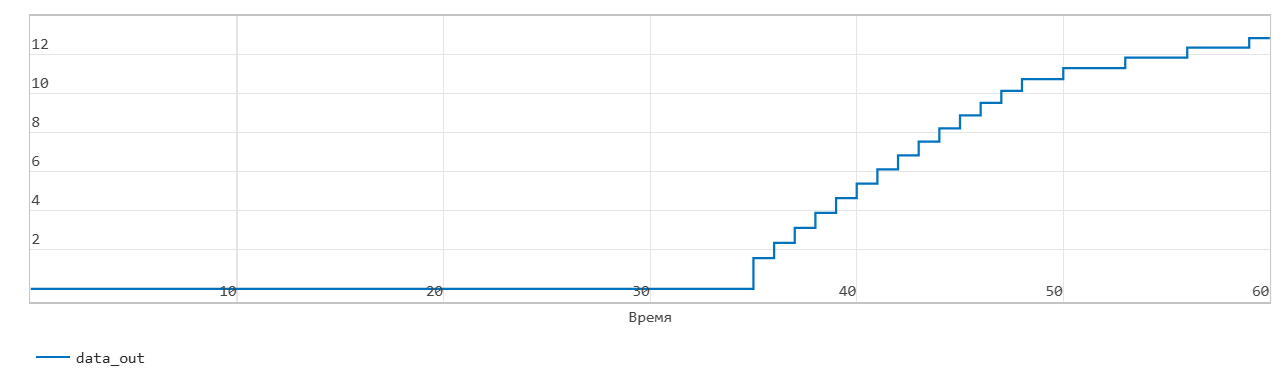

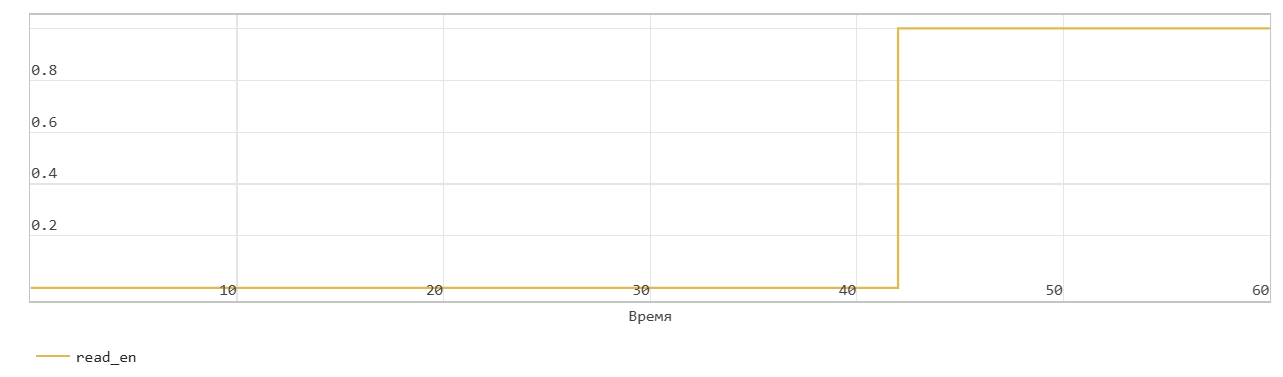

具有首字转换的FIFO读操作

此图显示了*Mode*参数设置为时的读取操作 FWFT. *Pop*输入端口作为读操作的使能信号。 在图中,*read_en*表示此信号。

在FWFT模式下,写入FIFO的第一个值将到达输出信号*Out*。

在图中,*read_en*变为等于 1 在时间步 42 FIFO在时间步长中读取*data out*信号的第一个值 9. 您可以利用此机会向前看并查看首次写入FIFO的数据。

当*Num*信号变得相等 0,给出*空*信号。 后*空*信号变为相等 0 如果从FIFO读取更多数据,则该块生成警告。